핵심 요약

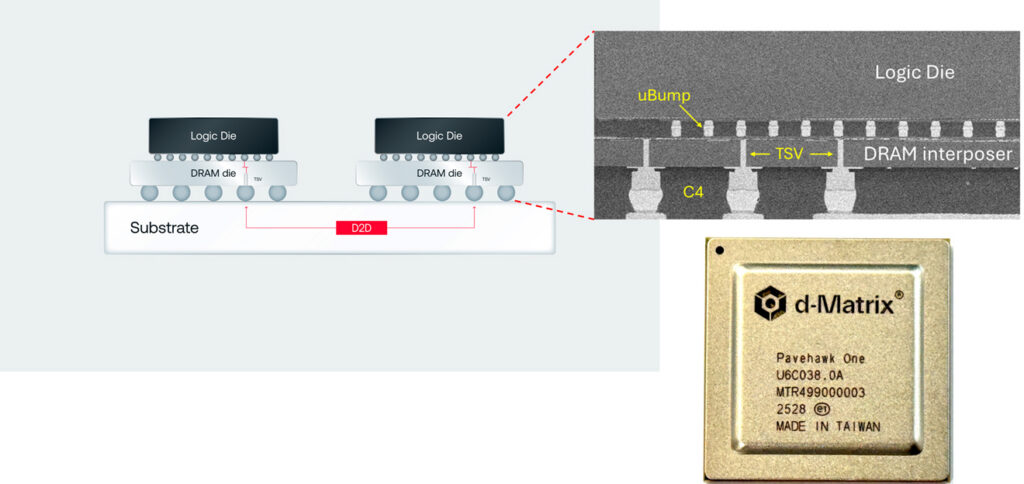

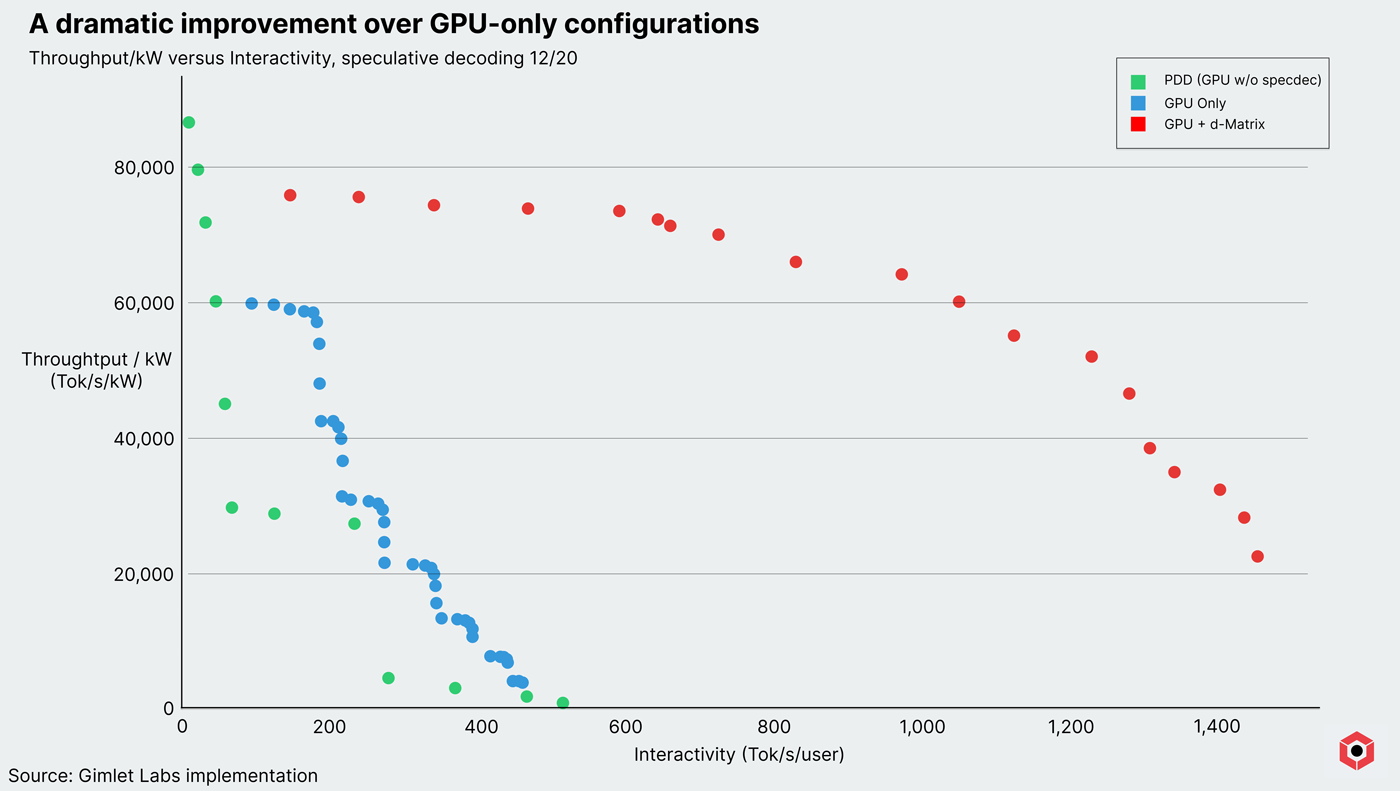

AI 추론의 핵심 병목인 메모리 용량과 대역폭 문제를 해결하기 위해 d-Matrix가 수직 적층 기술인 3DIMC를 도입했다. 기존 SRAM 기반 Corsair 아키텍처의 저지연성을 유지하면서 로직 다이 위에 DRAM을 직접 쌓아 HBM4 대비 10배 높은 20TB/s의 대역폭과 10배 뛰어난 전력 효율을 달성했다. 테스트 칩인 Pavehawk를 통해 기술적 타당성을 입증했으며, 이는 차세대 가속기 Raptor의 핵심 기반이 된다. 대규모 언어 모델과 복잡한 에이전트 파이프라인 처리에 최적화된 하드웨어 솔루션을 지향한다.

배경

SRAM 및 DRAM의 물리적 특성 차이, HBM(High Bandwidth Memory) 아키텍처에 대한 이해, 칩렛(Chiplet) 및 3D 패키징 기술 기초 지식, LLM 추론 시 발생하는 메모리 병목 현상에 대한 이해

대상 독자

AI 인프라 설계자, LLM 추론 최적화 엔지니어, 차세대 반도체 아키텍처 연구원

의미 / 영향

이 기술은 HBM의 물리적 한계를 뛰어넘는 새로운 메모리 아키텍처를 제시하여 LLM 추론 비용을 획기적으로 낮출 수 있습니다. 특히 전력 효율과 대역폭을 동시에 10배 개선함으로써 데이터 센터의 전력 밀도 문제를 해결하고 실시간 상호작용이 필요한 AI 에이전트 서비스의 대중화를 가속화할 것입니다.

섹션별 상세

실무 Takeaway

- 에이전트 파이프라인과 대규모 추론 모델의 메모리 병목을 해결하기 위해 HBM4를 능가하는 20TB/s 대역폭의 3D 적층 DRAM 도입이 필수적이다.

- 3DIMC 기술을 적용하면 비트당 전력 소비를 0.4pJ 이하로 낮추어 기존 솔루션 대비 전력 효율을 10배 개선하고 운영 비용을 절감할 수 있다.

- SRAM의 저지연성과 DRAM의 고용량을 결합한 칩렛 설계는 차세대 AI 가속기 Raptor의 핵심 경쟁력이 되어 분산 추론 성능을 극대화한다.

AI 요약 · 북마크 · 개인 피드 설정 — 무료